Vrcholem nabídky obvodů typu FPGA v nabídce firmy Lattice je řada SC, výrobcem označovaná jako Extreme Performance (Extrémní výkon). A v porovnání s ostatními FPGA, opravdu tato řada patří do té nejvyšší třídy programovatelných hradlových polí. Dle struktury chipu, popsané níže, je primárně určen pro velmi rychlou komunikaci všeho druhu s velkými objemy dat. K tomu je zapotřebí hlavně výkonné sériové komunikační kanály, tzv. SERDES s PCS, obvody podpory fyzické vrstvy většiny komunikačních standardů, a velká vnitřní integrovaná paměť v řádu alespoň jednotek MB. To vše FPGA LatticeSC nabízí.

Použití

- Aplikace zpracování signálů ze senzorů + vizualizace, přenos, zálahování

- HMI (Human-Machine Interface) - LED a LCD displeje a monitory, klávesnice, myš atd.

- Routery, Servery, Gateway

- Bezdrátové (Wireless) aplikace - WiFi, modemy

- Paměťová rozhraní SRAM, SDRAM, DDR

- Komunikační rozhraní mezi IrDA, UART, I2C, SPI, LPT, PCI

- Rozhraní pro paměťové karty, různé mechaniky

- Měřící zařízení - paralelní zpracování dat z desítek kanálů současně + vizualizace a zálohování dat

- Zpracování obrazu - MPEG-2, MPEG-4

- Zpracování zvuku - MP3, odšumování, zvýraznění, filtrace, digitální ekvalizér, apod.

- Zdravotnictví - zpracování EEG, EKG, zobrazení, řízení

- Komprese dat - ztrátová/bezeztrátová

- Převod komunikačních signálů mezi standardy

- Navigační systémy - GPS

LatticeSC - Architektura obvodu

Celou strukturu obvodu FPGA řady SC lze rozdělit do následujících bloků:

- Programmable Function Unit (PFU) - programovatelné logické a sekvenční bloky

- sysMEM Embedded Block RAM (EBR) - paměťové bloky s jednoduchým a duálním přístupem

- sysCLOCK s PLL a DLL - bloky generování hodinových a řídících signálů

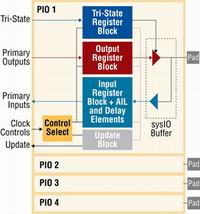

- Programmable I/O Cells (PIC) - vstupní/výstupní bloky podporující DDR přenos dat s pamětí

- sysCONFIG port - sériová a paralelní komunikace SPI, JTAG, atd.

- SERDES a PCS - bloky pro vysokorychlostní přenos a zpracování dat

- ASIC bloky MACO - hardwarové bloky s již specifickou funkcí

Obr. 1. Bloková struktura obvodu FPGA Lattice EC

PFU a EBR jednotka

Základ struktury tvoří aritmeticko-logické jednotky zvané PFU, které lze najít i na chipu nižších a levnějších řad EC, ECP2 nebo XP. Každá tato jednotka zde je složena ze čtyř vrstev obsahující dvě čtyřvstupé LUT tabulky (Look Up Table) a dva výstupní D klopné registry pro držení aktuálního stavu na výstupu. Na jednu PFU, obsahující i několik vývodů pro hodinové a řídící signály, tak připadá 53 vstupů a 25 výstupů. Ty lze prostřednictvím tříúrovňového systému propojovacích linek rychle propojit s ostatními okolními jednotkami. Navíc každá PFU může vytvořit 16x2 bitovou paměťovou buňku, která je součástí tzv. distribuované RAM nebo ROM. Při využití více jak 115 tisíců PFU, které se mohou na chipu vyskytovat, lze vytvořit blok paměti i přes 1 MB. K uložení dat jsou zde i 18 kb bloky dual port RAM paměti označené jako sysMEM EBR, které lze nakonfigurovat i jako paměť FIFO. Jejich souhrnná kapacita EBR může dosahovat až 7.3 MB při rychlosti přístupu 500 MHz.

Obr. 2. Možné konfigurace jednoteky PFU, resp. PFF

sysCLOCK PLL (Phase Locked Loops)

K úspěšnému využití FPGA jsou životně důležité zdroje hodinových signálů, které synchronizují celý chod. Proto jsou na chipu sysCLOCK jednotky obsahující PLL a DLL, z nichž může být signál šířen až po 12 vyhrazených rychlých linkách pro každý kvadrant integrovaného obvodu. Osm smyček fázových závěsů (Phase Locked Loop) umožňuje generovat široký rozsah frekvencí 15 MHz až 1GHz z externích signálů přivedené na vstupy Primary clock nebo Edge clock input. Spread Spectrum block umožňuje plynulou modulaci výstupního signálu. Dvanáct smyček digitálních závěsů (Digital Locked Loop) umožňuje korigovat zpoždění, jitter a přesně zastavovat a spouštět hodinové signály o frekvencích 100 až 700 MHz v případě velmi přesného časování. Externí signály lze také přímo šířit ze vstupů přes přesné děličky frekvence a multiplexery.

Komunikace FPGA s okolím

Hlavní doménou tohoto špičkového FPGA a hlavní výhodou proti ostatním, je jeho schopnost velmi rychlé a univerzální komunikace prakticky s čímkoliv, co podporuje nějakou formu paralelní nebo sériové komunikace. Pro velmi rychlou paralelní přenos dat slouží PIC bloky, pro tradiční sériovou komunikaci FPGA s jinými obvody pak SPI, JTAG a PowerPC bus a pro vytvoření velkoobjemových a velmi rychlý sériových kanálů (Gigabitový Ethernet, PCI Express apod.) jsou na chipu SERDES ve spojení s PCS.

sysCONFIG port

Pod tímto názvem se vyskytuje komunikační blok podporující SPI i JTAG standard, sériovou i paralelní komunikaci, dle nastavení. Umožňuje tak jednoduchou vzájemnou komunikaci mezi různými FPGA nebo MCU. SPI rozhraní lze použít k připojení SPI Serial FLASH BOOTovací paměti pro samotné nahraní programu do FPGA při jeho zapnutí (připojení napájení). To nabízí tyto FPGA jako jedni z prvních na světě.

Obr. 5. Pozice každého vstupního/výstupního bloku lze optimalizovat s ohledem na co nejmenší zpoždění průchodem dat

PICKe paralelní komunikaci a přenosu dat s vnějším okolím slouží PIC jednotky (Programmable I/O Cells), které jsou založeny na tzv. PURESPEED technologii. Ta je tvořena velmi rychlými buffery, umožňuje paralelní komunikaci FPGA s jinými externími obvody rychlostí až 2 Gb/s. To zajišťuje podporu DDR přenosu dat 2GB/s a až 1Gb/s v případě SDR, včetně generování časování a bufferování pro snadné připojení DIMM SDRAM paměťových modulů podporující DDR i DDR2 (Double Data Rate) přenos rychlostí až 800 MHz. Samozřejmostí je široká podporu všech běžných standardů pro úrovně logických signálů, jako jsou SSTL, LVTTL, HSTL, LVCMOS, PCI a nejnověji i AGP ve verzi 1x a 2x. |

Obr. 6. Blokové schéma jednotky PIC |

SERDES a flexiPCS

K stále užívanější vysokorychlostní sériové komunikaci slouží tzv. SERDES (Serializer-DeSerializer) bloky. Ty obecně pracují jako rychlé převodníky plně duplexní sériové komunikace na paralelní signály více vhodné pro zpracování v FPGA. Až 32 sériových kanálů může přenášet data rychlostí v rozsahu 600 Mb/s až 3.4 Gb/s s velmi nízkým jitterem při vysílání a velkou tolerancí jitteru při příjmu. Každý SERDES kanál může být uvnitř dále napojen na multiprotokolovou jednotku PCS (Physical Coding Sublayer), zde označovanou také jako flexiPCS, nebo případně přímo na logické buňky. SERDES a PCS pak dohromady tvoří výkonný modul realizující přenos dat na úrovni fyzické vrstvy OSI modelu v různých komunikačních protokolech. Seznam možného nastavení zahrnuje například SONETu (STS-12/STS-12c, STS-48/STS-48c), Gigabitový Ethernet (kompatibilní se specifikací IEEE 1000BASE-X), 10GbE (XAUI) 1.02 nebo 2.04 Gb/s optovláknový kanál, PCI-Express, nebo tzv. Serial RapidIO.

Obr. 7. Použití SERDES a PCS - většina operací zpracování signálů kom. protokolů je již implementována v PSC a není je nutné programovat

Strukturované bloky

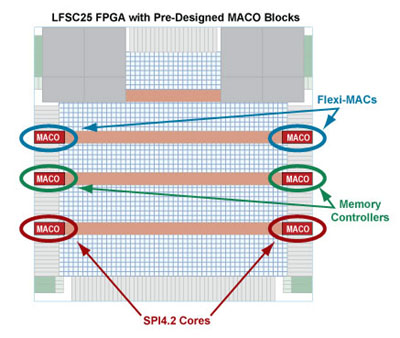

Poslední zajímavou částí chipu jsou strukturované ASIC bloky označené jako MACO (Masked Array for Cost Optimization). Ty mohou realizovat různé algoritmy aplikace a jejich výkon lze výpočetně přirovnat k asi 5 tisícům LUT, to vše ale asi na 10x menším prostoru. V rámci rozšířené řady SCM tyto bloky již obsahují předdefinovaná jádra průmyslových IP komunikačních standardů. To výrazně zjednodušuje návrh aplikací průmyslové komunikace a i samotné zpracování přenášených dat samotným FPGA.

Obr. 8. Předdefinované hardwarové ASIC MACO bloky pro zjednodušení zpracování signálů a dat

Vývojové prostředky & Evaluation Board

Pro

vývoj a ladění programu zůstává tradiční JTAG a vývojové prostředí pro PC označeném

jako ispLEVER 5.1 Service Pack 2, který je shodný pro všechny typy FPGA i další

programovatelné obvody Lattice. Software poskytuje vše potřebné pro rychlý a

úspěšný návrh a implementaci aplikace (syntézu, verifikaci a simulaci, Fitting,

Place & Route i naprogramování FPGA). K dispozici jsou samozřejmě i vývojové

kity a podpora programování již výrobcem vytvořenými bloky realizující konkrétní

algoritmus, tzv. ispLeverCore Intelectual Property . Tak lze přímo na chipu

bez programování vytvořit například rozhraní PCI, PCI Express, DMA, FCRAM, DDR

SDRAM Controller a mnoho dalších nebo algoritmy FFT, Reed-Solomon Encoder, FIR,

Viterby decoder atd.

Pro

vývoj a ladění programu zůstává tradiční JTAG a vývojové prostředí pro PC označeném

jako ispLEVER 5.1 Service Pack 2, který je shodný pro všechny typy FPGA i další

programovatelné obvody Lattice. Software poskytuje vše potřebné pro rychlý a

úspěšný návrh a implementaci aplikace (syntézu, verifikaci a simulaci, Fitting,

Place & Route i naprogramování FPGA). K dispozici jsou samozřejmě i vývojové

kity a podpora programování již výrobcem vytvořenými bloky realizující konkrétní

algoritmus, tzv. ispLeverCore Intelectual Property . Tak lze přímo na chipu

bez programování vytvořit například rozhraní PCI, PCI Express, DMA, FCRAM, DDR

SDRAM Controller a mnoho dalších nebo algoritmy FFT, Reed-Solomon Encoder, FIR,

Viterby decoder atd.

Pro

testování nových aplikací je možné využít několika typů vývojových desek (Evaluation

Boards) , které mimo FPGA poskytují i další periferie jako například oscilátor,

FCRAM, PCI Express, SMA a SPI konektory, DDR SDRAM rozhraní (konektor), konektor

RJ45, diody LED, přepínače apod.

Pro

testování nových aplikací je možné využít několika typů vývojových desek (Evaluation

Boards) , které mimo FPGA poskytují i další periferie jako například oscilátor,

FCRAM, PCI Express, SMA a SPI konektory, DDR SDRAM rozhraní (konektor), konektor

RJ45, diody LED, přepínače apod.

Závěr

FPGA řady SC, které jsou nabízena v pouzdrech typu BGA (fpBGA, ffBGA, fcBGA) ve velkém rozsahu počtu I/O vývodů (132 až 962), lze objednat u distributora integrovaných obvodů Lattice v České republice, firmy HT-Eurep Electronics. Tu je možné kontaktovat prostřednictvím webových stránek - www.hte.cz. Podrobné informace i katalogové listy lze pak přímo získat na stránkách firmy Lattice - www.latticesemi.com.

Antonín Vojáček

vojacek@ hwg.cz

DOWNLOAD & Odkazy

- Domovská stránka českého distributora firmy HT Eurep - http://www.hte.cz

- Domovská stránka Lattice Semiconductor - http://www.latticesemi.com

- podrobný datasheet LatticeSC (203 stran)

- článek o FPGA MachXO

- článek o Lattice

EC & ECP na HW serveru